随着EDA技术的发展,使用硬件语言设计PLD / FPGA已成为一种趋势。目前最重要的硬件描述语言是VHDL和Verilog HDL。

VHDL早期开发,语法严格,Verilog HDL是基于C语言开发的硬件描述语言,语法相对自由。与Verilog相比,VHDL和Verilog HDL比Verilog更加繁琐,但verilog的免费语法也很容易让一些初学者犯错误。

许多外国电子专业的学生在本科阶段教授VHDL,在研究生阶段教授verilog。从国内的角度来看,VHDL有很多参考书,很容易找到数据,而Verilog HDL的参考书相对较少,这给学习Verilog HDL带来了一些困难。

从EDA技术的发展出现了用于CPLD / FPGA设计的硬件C语言编译软件。虽然它仍然不成熟并且应用很少,但它可能成为继VHDL和Verilog之后的大规模CPLD / FPGA。

另一种手段。

(1)与其他硬件描述语言相比,VHDL具有更强的行为描述能力,这决定了他是系统设计领域最好的硬件描述语言。

强大的行为描述功能是避免特定设备结构以及从逻辑行为描述和设计大规模电子系统的重要保证。 (2)VHDL丰富的仿真语句和库函数可以在任何大型系统设计的早期阶段检查设计系统的功能可行性,并随时模拟设计。

(3)VHDL语句的行为描述能力和程序结构决定了他具有支持大规模设计的分解和现有设计的重用功能。满足市场需求的大规模系统是高效的,并且高速完成必须由多个人甚至多个并行工作的多个组执行。

(4)对于使用VHDL完成的特定设计,EDA工具可用于逻辑综合和优化,VHDL描述设计自动转换为门级网表。 (5)VHDL具有相对独立的设计描述。

设计人员无需了解最终设计的结构即可理解硬件结构。 HDL有两个用途:系统仿真和硬件实现。

如果程序仅用于模拟,则几乎可以使用所有语法和编程方法。但是,如果我们的程序用于硬件实现(例如,用于FPGA设计),那么我们必须确保程序是“可集成的”。

(程序的功能可以在硬件电路中实现)。在软件合成期间,将忽略或报告不可集成的HDL语句。

我们应该记住,“所有HDL描述都可用于模拟,但并非所有HDL描述都可以在硬件中实现。使用VHDL / VerilogHD语言开发PLD / FPGA的完整过程如下:1。

文本编辑:使用任何文本可以使用编辑器,也可以使用专用的HDL编辑环境。通常,VHDL文件保存为.vhd文件,Verilog文件保存为.v文件。

2.功能仿真:将文件加载到HDL仿真软件中进行功能仿真,并检查逻辑功能。它是否正确(也称为预仿真,这个步骤可以跳过简单的设计,只有在接线完成后,时序仿真)3。

逻辑综合:将源文件传输到逻辑综合软件进行综合,即,语言被集成到最简单的布尔表达式和信号连接关系中。逻辑综合软件将生成.edf(edif)的EDA行业标准文件。

4.布局布线:将.edf文件传输到PLD制造商提供的软件进行布线,即设计良好的逻辑放置在PLD / FPGA中。 5.时序仿真:需要利用布局和布线确认参数,用仿真软件验证电路的时序。

(也称为后仿真)6。程序下载:在确认仿真正确后,将文件下载到芯片HDL与传统的原理图输入方法之间的关系就像高级语言和汇编一样。

语言之间的关系。 HDL便携且易于使用,但效率不如原理图;原理图输入的可控性好,效率高,相对直观,但设计大规模CPLD / FPGA非常麻烦,便携性差。

在实际的PLD / FPGA设计中,通常建议使用原理图和HDL的组合进行设计,原理图适用于原理图,而HDL适用于HDL。没有强制性规定。

当时,我们的最终目标是使用我们最熟悉的工具设计高效,稳定且满足设计要求的电路。硬件描述语言HDL已经开发了20多年,并已成功应用于每个设计。

阶段:建模,模拟,验证,综合等。它出现在20世纪80年代。

数以百计的硬件描述语言极大地促进和促进了设计自动化。但是,这些语言通常面临特定的设计领域和级别,许多语言使用户感到茫然。

因此,迫切需要一种取向。采用多域,多层和广泛接受的标准硬件描述语言设计。

在20世纪80年代后期,VHDL和Verilog HDL语言适应了这一趋势并成为IEEE标准。现在,随着系统级FPGA和系统随着芯片的出现,硬件和软件协调设计和系统设计变得越来越重要。

传统意义上的硬件设计越来越倾向于与系统设计和软件设计相结合。硬件描述语言迅速发展以适应新的情况,并出现了许多新的硬件描述语言,如Superlog,SystemC,Cynlib C ++等。

公司: 深圳市捷比信实业有限公司

电话: 0755-29796190

邮箱: ys@jepsun.com

产品经理: 李经理

QQ: 2057469664

地址: 深圳市宝安区翻身路富源大厦1栋7楼

更多资讯

获取最新公司新闻和行业资料。

- WAN8060NU37H06 vs WAN8060NU68H06:从硬件到用户体验的全面评测 前言:为何要关注这两款路由器?随着家庭网络设备数量激增,路由器的性能瓶颈日益显现。华为推出的WAN8060NU系列正是应对这一挑战的产物。而在这其中,WAN8060NU37H06与WAN8060NU68H06因命名相似却性能差异明显,常引发用户困惑。...

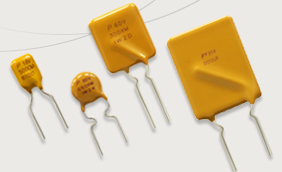

- PTTC聚鼎PT05D3CE与PT03D3CE在智能硬件中的应用实践 PTTC聚鼎PT05D3CE与PT03D3CE在智能硬件领域的实战应用随着物联网技术的发展,智能硬件对传感器模块的性能提出了更高要求。PTTC聚鼎的PT05D3CE与PT03D3CE作为高性能传感解决方案,已在多个智能硬件项目中成功落地。1. 智能家居温湿度...

- 深入解析WAN3216FD27H08与WAN3216FD27H06的硬件差异及选型指南 背景介绍随着工业物联网(IIoT)的快速发展,嵌入式控制器模块的选型愈发重要。WAN3216FD27H08与WAN3216FD27H06作为同一产品系列中的两个版本,虽命名相似,却在硬件设计上存在关键区别。本文将结合真实测试数据,详细剖析其差异...

- AMR传感器与MRAM:下一代智能硬件的核心技术突破 AMR传感器与MRAM:驱动智能设备革新的双引擎在现代电子技术快速演进的背景下,自旋电子学(Spintronics)正成为半导体产业的重要发展方向。其中,各向异性磁阻(Anisotropic Magnetoresistance, AMR)传感器与磁性随机存取存储器(Magne...

- 深度解析WAN2012K245HL5 vs H245C04:从硬件架构到实际部署的全面评测 前言:为何要进行跨型号对比?随着物联网设备日益多样化,不同型号之间的性能差异直接影响系统整体效率。本篇聚焦于两个典型代表——WAN2012K245HL5与H245C04,通过结构化对比揭示其在硬件设计、软件兼容性与现场部署中的真...

- 深入解析光颉精密电阻在智能硬件中的关键作用 深入解析光颉精密电阻在智能硬件中的关键作用随着物联网(IoT)、人工智能(AI)和智能终端设备的快速发展,对电子元器件的性能要求不断提升。在这一趋势下,光颉精密电阻以其出色的电气特性与环境适应能力,在智能硬件...

- 深度解析:PTTC聚鼎系列电阻在智能硬件中的应用实践 背景介绍随着物联网(IoT)和智能硬件的快速发展,电子元器件的小型化、高性能化已成为行业主流趋势。PTTC聚鼎凭借其自主研发的精密电阻技术,推出了包括PVR05D和PMV0402-5R5E5R0在内的多款高性能贴片电阻,广泛服务于智能家居...

- SDN系列功率电感器:工业级稳定表现助力智能硬件发展 SDN系列功率电感器的技术亮点与应用前景随着智能硬件向智能化、高稳定性方向演进,对电源组件提出了更高要求。SDN系列功率电感器应运而生,专为工业控制、车载电子及智能电网等严苛环境设计,展现出强大的耐久性与适应...

- PTTC聚鼎PT712M参数手册深度解读:从硬件到应用的最佳实践 PTTC聚鼎PT712M参数手册核心内容精析本文基于官方《PTTC聚鼎PT712M参数手册》对模块的关键特性进行深入解读,帮助开发者和技术人员快速掌握其使用要点与优化策略。1. 模块尺寸与封装设计外形尺寸:25mm × 25mm × 3.5mm,紧凑型设计...

- 深入解析WAN2614K245H04、WAN2012K245H02与H245C04的差异:从硬件到通信协议全面评测 前言:为何要对比这些型号?在实际工程项目中,同一类别的多个型号常常令人困惑。本文以WAN2614K245H04、WAN2012K245H02与H245C04为例,剖析它们在硬件设计、通信能力、环境适应性等方面的异同,助力精准选型。一、硬件结构与安装...

- ALPS卡座连接器技术革新:从硬件到智能协同的全面升级 ALPS卡座连接器的演进之路:从物理连接到智能协同ALPS卡座作为电子系统中不可或缺的接口组件,正经历从传统机械连接向智能化、网络化方向的深刻变革。结合PDCALPSTIA协同机制,其性能边界不断被突破。一、传统连接器的局限...

- 从硬件到云端:如何高效实现 ThunderBolt 切换器与 TIA Portal 及 MindSphere 的联动 从硬件到云端:如何高效实现 ThunderBolt 切换器与 TIA Portal 及 MindSphere 的联动随着工业4.0的深入发展,企业对“软硬一体”的集成化解决方案需求不断上升。要充分发挥 ThunderBolt 切换器在高速数据交换中的潜力,必须将其与西门子...

- 浪涌保护器的专业术语 1.空气终端系统 用于直接接受或承受雷电的金属物体和金属结构,如避雷针、避雷带(线)、避雷网等。 2.引下线系统 连接空气终端和接地装置的金属...

- ‘光颉光颉’网络用语爆火背后:从品牌名到梗文化的演变 从企业名称到网络迷因:‘光颉光颉’的传播现象分析近年来,“光颉光颉”这一原本属于电子元器件品牌“光颉科技”的名称,意外成为中文互联网上的热门网络用语。它最初源于网友对品牌发音的戏仿,逐渐演变为一种带有...

- 弥尔曼定理陈述 在该定理中,电路图可以修改为具有分支的并联网络,其中每个分支都包含一个电阻器或电压源与电阻器的组合。米尔曼定理仅适用于可以相应重新绘制的电路。这里,米尔曼定理的示例电路如下所示。米尔曼定理电路为了应用...

- 0.22μF电容参数概述 0.22μF(微法拉)电容是一种常用的电容器件,其主要参数包括电容量、额定电压、允许偏差、工作温度范围等。对于0.22μF电容而言,常见的额定电压有6.3V、10V、16V、25V、50V等,用户需根据实际应用场合选择合适的电压等级。在...

- 电容元件是耗能原件吗 电容,电阻,电感是最常见的电子元件,应用广泛。 电容,电阻,电感基本概念如下:(1) 电感器:一种可以将电能转换为磁能并将其储存的部件。电感器的结构与变压器相似,但只有一个绕组。电感器具有一定...

- LF10气压开关:应用与功能概述 LF10气压开关是一种精密的设备,用于监测和控制特定环境或系统中的气压水平。这种类型的开关广泛应用于各种工业、医疗和其他需要精确气压控制的领域。在工业环境中,例如,在压缩空气系统中,LF10气压开关可以确保机器在...

- 2W功率贴片电阻R5系列概述 2W功率贴片电阻R5系列是专为高功率应用设计的电子元件。此类电阻器采用贴片形式,便于自动化生产和电路板布局。R5系列电阻具有2瓦特的额定功率,这意味着它们可以处理较高的功率负载而不会过热或损坏。这类电阻器广泛应...

- ALPS阿尔卑斯开关全系列产品概述 ALPS阿尔卑斯开关作为行业内的知名品牌,提供了一系列高品质的产品以满足不同用户的需求。其全系列产品包括了多种类型的开关,如轻触开关、拨动开关、检测开关等,广泛应用于汽车电子、家用电器、通讯设备等多个领域。...