SOC的定义有很多种。通常,SOC是基于处理器的IC,包含一个或多个嵌入式计算引擎(微处理器,微控制器或数字信号处理器);工艺技术;主要使用第三方IP核进行设计;内置嵌入式存储器和可编程逻辑;与芯片的外部编程;完整系统所需的全部或大部分外围设备。

在某些情况下,它还包括在同一芯片上集成了模拟和数字技术的模拟前端,增加了系统的复杂性。传统的设计过程可分为两个独立的阶段:逻辑设计和物理实现,包括以下步骤:系统规划,功能设计,逻辑设计,电路设计,设计验证,生产生产,测试调试和芯片设计考虑都很简单。

。所有设计人员必须做的是前端设计,例如系统架构设计,前端仿真和硅供应商的网表(SIC)。

硅供应商负责后端设计,包括芯片的物理设计,封装,测试和良率管理。然而,随着系统集成的不断完善和最终用户需求的多样化,系统功能越来越复杂。

如何确定系统结构,完成软硬件的划分,传统的系统设计方法不能很好地满足设计要求。为了提高芯片的设计效率,缩短设计周期,系统设计需要一种新的设计理论体系和设计方法,以克服传统设计方法中前端设计和后端设计的缺点。

这种新的设计理论和设计方法得到了硬件和软件协同设计理论,IP核生成和多路复用技术以及超深亚微米技术的支持。 SOC开发最具挑战性的方面是设计验证。

使用相应的测试向量开发一个或一组测试平台是耗时的。根据需要对结果进行仿真和分析不仅需要大量的计算资源,还需要对设计行为进行相当深入的理解。

统计3表明,验证是产品开发中最耗时的方面之一,它需要最多的资源。提供IP内核的供应商和系统设计人员面临严重的验证问题。

制造商不仅要彻底检查核心的性能和物理特性,以确保产品质量,还要预测系统级功能。设计人员必须开发功能级测试方法,以模拟设备的正确使用和误用。

为模拟错误开发有效的测试方法更加困难,因为预测误解和意外错误需要仔细研究技术规范。除了验证之外,SOC测试尤其困难。

需要新的测量功能和测试方法,以确保产品具有足够的设计公差。这需要内置自测(BIST)和边界扫描链结构。

许多IP公司提供BIST架构和边界扫描IP以及自动化软件工具,以支持设计人员采用这些技术。对于BIST方法,最大的优势是整体测试覆盖率,测试价格和测试时间。

从很大程度上说,SOC芯片包含:1。逻辑内核包括CPU,时钟电路,定时器,中断控制器,串行并行接口,其他外设,I / O端口以及各种IP内核之间的连接。

逻辑等; 2.存储器核心包括各种易失性,非易失性和Cacha存储器; 3.模拟内核包括用于某些高速电路的ADC,DAC,PLL和模拟电路。

公司: 深圳市捷比信实业有限公司

电话: 0755-29796190

邮箱: ys@jepsun.com

产品经理: 李经理

QQ: 2057469664

地址: 深圳市宝安区翻身路富源大厦1栋7楼

更多资讯

获取最新公司新闻和行业资料。

- 欧璐O-墙壁开关:简约设计与实用功能的完美结合 欧璐O-墙壁开关是一款结合了实用性和设计感的产品,特别适合现代家居使用。这款开关设计为一开多三孔单的设计模式,意味着一个开关可以控制多个电器的电源,不仅节省了安装空间,还极大地提升了使用的便捷性。其外观简...

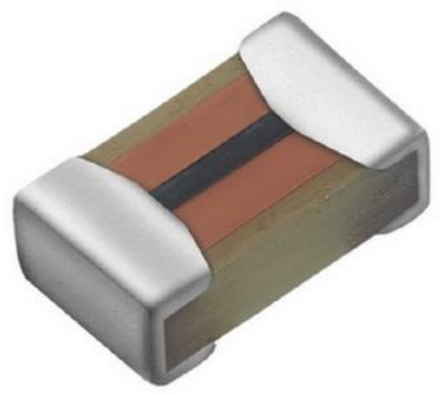

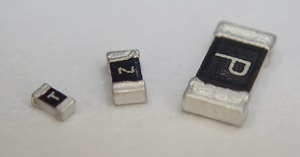

- 贴片电阻合芯片 片式固定电阻器,从Chip Fixed Resistor直接翻译过来的,俗称贴片电阻(SMD Resistor) ,是金属玻璃釉电阻器中的一种。是将金属粉和玻璃釉粉混合,采用丝网印刷法印在基板上制成的电阻器。耐潮湿和高温, 温度系数小。可大大节约电...

- 贴片合金电阻芯片底是绿色的 超低欧姆(金属条)贴片电阻器 - LR 系列 文件下载降额曲线LR 大功率 2512 3W、1206 1W、表面贴装功率金属条电阻器。电阻范围 0.5m-10mohm,批次 TC 为 50ppm。金属条低欧姆电阻,用于感应大电流,耐高温。低 TCR 可在高温下实现...

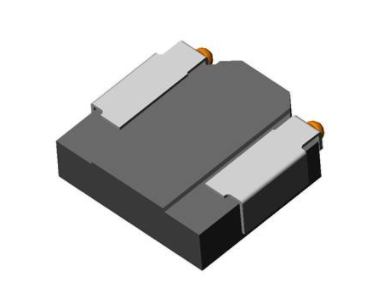

- 光颉Viking陶瓷多层片式电感器CL-S系列参数与应用详解 在现代电子设备中,电感器作为重要的被动元件之一,其性能直接影响着电路的工作效率和稳定性。光颉科技推出的Viking陶瓷多层片式电感器CL-S系列凭借其卓越的性能,在众多应用领域中脱颖而出。该系列产品具有高Q值、低直流...

- 光颉viking CL-S系列陶瓷多层片式电感器性能解析与应用优势 光颉viking CL-S系列陶瓷多层片式电感器:高性能电子元件的代表在现代电子设备日益小型化、高集成化的趋势下,对关键元器件的性能要求也不断提升。光颉viking推出的CL-S系列陶瓷多层片式电感器,凭借其卓越的电气性能和可靠...

- 光颉viking陶瓷多层片式电感器(CL-S系列):高性能高频应用的理想之选 光颉viking CL-S系列陶瓷多层片式电感器核心优势解析在现代电子设备日益追求小型化、高集成度与高效能的背景下,光颉viking推出的CL-S系列陶瓷多层片式电感器凭借其卓越的电气性能和可靠的稳定性,成为高频电路设计中的首选...

- 芯片电容 单层芯片电容器具有体积小、应用频率高、损耗低、电容大、微波性能优异、可焊性好等特点。它们广泛用于各种射频模块电路设计,如雷达、航空航天和航空,是射频和微波电路中必不可少的电子元件。&nbs...

- 点火芯片有电阻吗 雷管点火头,又叫点火桥丝、贴片桥丝,是一种发火装置,就像鞭炮的引信一样?不过它是通过电子雷管的模组控制的,模组控制电容充放电,大电流流过桥丝端子发热,从而起到引燃的作用。HT-TPQS系列的雷管点火头用的比较广...

- 单层芯片电容是什么 单层芯片电容器具有体积小、应用频率高、损耗低的特点,广泛应用于移动通信、雷达、航空航天等各种射频模块电路设计中,起到隔离、旁路、滤波、耦合等作用,是微波电路中必不可少的电子元件。单层芯片电容器属于无源...

- 冰箱启动器热敏电阻芯片 冰箱常用的起动器是PTC起动器和重锤式启动器。 PTC起动器是一种特殊的热敏电阻,其正常电阻值为18至30Ω。当电阻体被启动电流加热时,电阻体的电阻值迅速增加,并在高温下保持高电阻值。&...

- PTTC聚鼎PT2421NT芯片参数与应用解析 PTTC聚鼎科技作为国内知名的集成电路设计公司,其产品在电源管理领域有着广泛的应用。PT2421NT是PTTC推出的一款高性能开关电源控制芯片,主要应用于AC-DC转换器、适配器和充电器等设备中。这款芯片采用了先进的恒定导通时间...

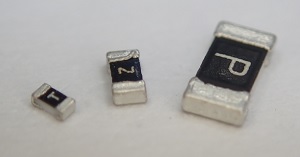

- SMD 0.8X0.8mm芯片参数及应用领域 在电子设计和制造领域,SMD(Surface Mount Device)贴片元件因其小巧轻便、便于自动化生产的特点而被广泛应用。特别是对于空间紧凑、集成度要求高的电路板设计来说,SMD元件是不可或缺的选择。以您提到的SMD 0.8X0.8mm尺寸的芯片...

- SMD 0.65X0.65mm芯片参数与应用解析 在电子设计和制造领域,选择合适的表面贴装器件(Surface-Mount Device, SMD)是确保电路板性能的关键。其中,尺寸为0.65x0.65毫米的SMD芯片因其小巧的体积,在高密度集成电路中扮演着重要角色。这类微型芯片通常用于移动设备、可...

- SMD 0.6X0.3mm芯片参数及应用领域 在现代电子工程领域中,SMD(Surface Mount Device)元件因其小巧、高效的特性而被广泛应用。您提到的SMD 0.6X0.3mm规格的芯片,是一种极为紧凑的表面贴装器件,通常用于高密度电路板设计。这类微小尺寸的芯片主要应用于手机、智...

- 如何根据需求选择WAN7020L039M04与WAN7020L245M04芯片? 基于应用场景的选型决策指南面对WAN7020L039M04与WAN7020L245M04这两款功能相近却各有侧重的芯片,工程师在选型时需综合考虑系统需求、成本预算和开发周期等因素。以下从多个维度提供详细建议。1. 功耗优先:选择WAN7020L245M04若项...

- SMD 1.6x0.8mm芯片参数与应用领域 在电子设计和制造领域,选择合适的表面贴装器件(SMD)对于确保电路板的功能性和可靠性至关重要。以SMD 1.6x0.8mm规格的芯片为例,这类小型化元件因其体积小、重量轻以及适合自动化生产的特点,在现代电子设备中得到广泛应...

- SMD 3.2x1.6mm芯片参数及应用领域 在现代电子技术快速发展的背景下,SMD(Surface Mount Device)贴片元件因其体积小、重量轻、便于自动化生产等优点,在电子产品中得到了广泛应用。其中,SMD 3.2x1.6mm规格的芯片作为一种常见的贴片元件,广泛应用于各类消费电子...

- PTTC聚鼎PT3621NT芯片参数与应用详解 在现代电子技术飞速发展的今天,各种高性能集成电路被广泛应用于各类电子产品中。其中,PTTC聚鼎PT3621NT作为一款备受关注的芯片,凭借其卓越的性能和广泛的应用领域,在市场上占据了重要地位。本文将深入探讨PTTC聚鼎PT362...

- PT712M PTTC聚鼎芯片参数与应用详解 在现代电子设备中,芯片作为核心组件起着至关重要的作用。PT712M是PTTC聚鼎推出的一款高性能芯片,它凭借其卓越的性能和稳定性,在多个领域得到了广泛应用。接下来,我们将详细介绍PT712M的主要参数、特点以及应用场景。##...

- PTTC聚鼎PT1521NT芯片参数与应用领域 在现代电子设备中,集成电路扮演着至关重要的角色。其中,PTTC聚鼎科技推出的PT1521NT芯片是一款高性能、低功耗的产品,在众多领域都有广泛的应用。这款芯片集成了先进的技术,能够满足不同应用场景下的需求。它主要应用...